"NVIDIA ‘Accidentally Damages‘ a Chip"

PCIe Retimer的“foundation of existence”

To understand Retimer chips, we first need to understand the PCIe bus.

As is widely known, a bus serves as the "road" for data communication between different hardware components on a computer/server motherboard. The amount of data transmitted per unit time is

called bandwidth, which is measured in bits per second. The bus plays a decisive role in the speed of data transmission between hardware components. Against the backdrop of ever-increasing

requirements for computing speed and latency in servers, computer bus standards are also constantly evolving.

Currently, the most mainstream bus is the PCIe protocol (PCI-Express), which was proposed by Intel in 2001 to replace older bus standards such as PCI, PCI-X, and AGP. In recent years, the PCIe protocol

has developed rapidly, with its transmission rate basically doubling every 3-4 years while maintaining excellent backward compatibility.

Especially in today's era of explosive growth in artificial intelligence (AI) computing power demand, high-speed data transmission within data centers is facing unprecedented pressure. This has driven

the rapid development of the PCIe protocol, which has advanced from PCIe 3.0 and 4.0 to the 5.0 and 6.0 generations, with transmission rates doubling continuously from 8GT/s and 16GT/s to 32GT/s and 64GT/s.

However, as communication rates increase generation by generation, the problem of signal attenuation has become increasingly severe. In the iteration of PCIe standards, on one

hand, the continuous development of applications drives the iterative update of PCIe standards, doubling the speed constantly; on the other hand, the physical size of servers is

limited by industry standards and has not changed significantly. This has led to a rise in the insertion loss of the entire link—from 22dB in the PCIe 3.0 era to 28dB in the PCIe 4.0

era, and further to 36dB in the PCIe 5.0 era. How to solve the insertion loss problem of PCIe signal links and increase the PCIe signal transmission distance has become a crucial

issue for the industry.

The emergence of Retimers is an inevitable outcome of PCIe development reaching a certain stage. Before PCIe 4.0 and earlier versions, the data transmission rate was relatively low, and the requirements for signal integrity were not high. But in the PCIe 5.0 and PCIe 6.0 eras, with data transmission rates rising to 32GT/s and 64GT/s, problems such as signal

attenuation and jitter have become increasingly prominent, and insertion loss has increased accordingly.

The PCIe specification has a precise insertion loss budget. For example, the insertion loss budget of the PCIe 6.0 version is 32dB, which means that during the design process, it is

necessary to ensure that the total loss of the signal during transmission does not exceed 32dB to maintain signal quality.

In response to this, PCIe Retimer chips have become the mainstream solution to address the signal attenuation problem.

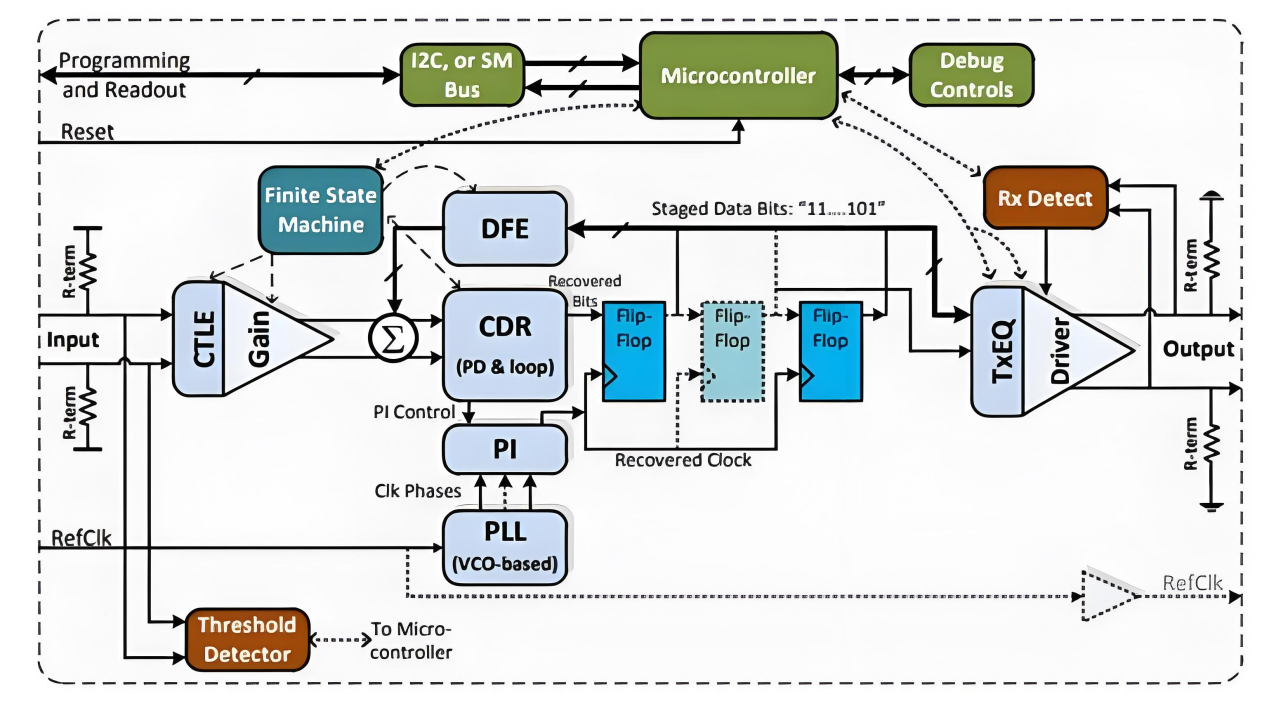

A Retimer chip is a mixed-signal analog/digital chip. Its working principle is to use an internal clock recovery circuit to re-time the input signal, thereby eliminating clock offset and

jitter, and correcting the phase and timing deviation (jitter) of the signal. It can extend the transmission distance of the interface and improve signal quality. PCIe Retimer chips

mainly solve issues such as irregular signal timing, high loss, and poor integrity when data centers and servers transmit data at high speeds and over long distances through the

PCIe protocol.

Internal structure of the Retimer chip (Image source: PCI-SIG official website)

Compared with other technical solutions in the market, the Retimer chip solution currently has certain comparative advantages in terms of performance, standardization, and

ecosystem support. It is worth mentioning that Retimer chips can flexibly switch between PCIe or CXL modes, which is more in line with the future CXL interconnection trend.

This functional feature endows it with inherent high value in the general-purpose server and AI server markets.

In the field of general-purpose servers, with the expansion of cloud computing and big data centers, and the rapid increase in the penetration rate of servers with PCIe 5.0 and above

versions, each server needs to be equipped with 2-4 Retimer chips (for connecting CPUs to PCIe slots and high-speed storage). Combined with the growth of edge computing

servers, the market demand for Retimer chips is showing exponential growth.

In addition, with the rise of the AI wave, AI servers have become one of the main incremental application scenarios for Retimer chips.

It is understood that the number of PCIe Retimer chips in an AI server is directly related to the number of GPUs configured in the server. This is because the number of lanes of the

GPU directly determines the ratio of PCIe links.

AI servers usually require multiple GPUs to work together for computing. A single AI server is often equipped with 4-8 or even more GPUs. The PCIe links between GPUs and CPUs, as

well as between GPUs themselves, are not only long but also need to transmit massive amounts of training data simultaneously. Retimer chips are precisely the key to breaking the

"signal bottleneck of multi-GPU interconnection" and can significantly improve the collaboration efficiency of AI computing clusters.

At present, a typical mainstream AI server equipped with 8 GPUs requires 8 or even 16 PCIe 5.0 Retimer chips.

It is evident that Retimer chips have broad market space in the AI era and the server field.

Duopoly leads and multiple strong players compete for the "golden track"

In the golden age of PCIe high-speed interconnection, the Retimer chip market has formed a pattern of "led by a duopoly and competed by multiple strong players".

Currently, the global market is mainly divided by server analog-digital chip manufacturers and traditional analog giants. Among them, the competition between AsteraLabs and

Montage Technology is particularly notable—the former occupies a major global share by virtue of its first-mover advantage in PCIe 5.0, while the latter is rapidly rising with the

momentum of domestic substitution, and the two jointly dominate the high-end market. Pericom and IDT (acquired by Renesas) occupy traditional positions relying on their

technical accumulation, while giants such as TI and Microchip cover the mid-to-low-end fields with general-purpose products, forming a multi-level competitive ecosystem.

Tracing back the development process, the technical paths of different manufacturers show distinct differences.

As an early entrant in the market, Pericom, relying on its first-mover advantage in the PCIe 3.0/4.0 era, was the first to have its products certified by mainstream platforms such as

Intel and AMD, becoming a core supplier for server manufacturers. Currently, it has formed a complete product line covering PCIe 3.0-5.0, and the transmission rate and low-latency

characteristics of its related chips have secured a firm position in the high-end market.

IDT, on the other hand, relied on its technical accumulation in the field of timing chips and had an advantage in multi-generational PCIe protocol compatibility in the early days.

After being acquired by Renesas, its Retimer technology was deeply integrated with Renesas' analog chip capabilities, and it continues to expand into the PCIe 5.0/6.0 field.

The U.S. manufacturer AsteraLabs broke the tradition with the concept of "Smart Retimer". Its PCIe 4.0 products entered mass production in 2024, and its PCIe 5.0 products reduced

customers' upgrade costs through pin-compatible design. It also jointly established the Cloud-Scale Interop Lab ecosystem with cloud service providers, quickly seizing the AI

server market and becoming the current share leader in the 4.0/5.0 era.

Montage Technology, a domestic leader, has demonstrated strong substitution capabilities. After expanding from the memory interface chip field, its PCIe 4.0 Retimers have

achieved stable mass production. Shipments of its PCIe 5.0 products doubled for two consecutive quarters starting from 2024, with sufficient hand orders. Moreover, it took the

lead in launching PCIe 6.x/CXL 3.x Retimers and sending samples in early 2025, with a transmission rate of 64GT/s, further strengthening its technical barriers.

Traditional analog giants are capturing market shares through differentiated strategies. Leveraging its extensive industrial customer base, TI provides general-purpose Retimer

chips adaptable to multiple scenarios. Although it has not focused on the high-end AI field, it still maintains competitiveness in medium-and low-speed PCIe links. As early as 2020,

Microchip launched a Retimer series supporting PCIe 5.0 and CXL 2.0. Its products have become a common choice for Intel platform reference designs, securing a position in the

traditional server market.

Driven by the dual dividends of domestic substitution and technological upgrading, this competition centered on high-speed interconnection is entering a period of opportunities.

According to industry data forecasts, the global PCIe Retimer chip market size will reach 1.8 billion US dollars by 2025. Against this market potential, Retimer chips have been

regarded as a "must-have component under the wave of PCIe high-speed development" and a "golden track" in the semiconductor industry chain that is deeply bound to AI

computing power and server expansion.

nvtel alliance brings subtle changes

However, this technological revolution jointly initiated by NVIDIA and Intel may bring subtle changes to the PCIe Retimer market.

When NVIDIA strategically invested $5 billion in Intel and opened up its NVLink technology ecosystem, this long-term challenger to the PCIe standard finally gained a key fulcrum to reshape the industry structure. And Intel, as the founder of the PCIe protocol, chose to "switch sides," which further endows this impact with the in-depth power to subvert technical camps.

First, the overwhelming effect of technological generation gap takes the brunt. It is understood that the fifth-generation NVLink technology has achieved a total bandwidth of

1.8TB/s, which is more than 14 times that of PCIe Gen5. Moreover, it minimizes signal transmission loss through chip-level integrated design. This advantage directly undermines

the value of PCIe Retimers. For example, in NVIDIA's GB200 NVL72 rack system, 576 GPUs form an overall bandwidth of over 1PB/s through NVLink, enabling stable

interconnection without any signal compensation chips. In contrast, in traditional solutions, an 8-GPU AI server needs to be equipped with 8-16 PCIe 5.0 Retimers to avoid signal

distortion.

NVLink provides the x86 architecture with interconnection capabilities featuring higher bandwidth and lower latency than traditional PCIe, which may change the computing and data flow patterns inside data centers.

When Jensen Huang emphasized at the press conference that "the best CPU and the best GPU should be combined through NVLink," he actually declared the end of the "compensation era" in the field of high-speed interconnection.

More critically, NVIDIA GPUs hold absolute dominance in the AI era. They account for 92% of the discrete graphics card market, their share in the PC GPU market has also risen to

24%, and the AI training scenario is almost entirely dependent on its chips. In the data center field, customized NVLink x86 CPUs will replace universal PCIe interface solutions; in

the personal computing field, Intel's SoCs integrated with RTX GPU chiplets will reduce reliance on discrete PCIe graphics cards.

On the other hand, the main function of Retimer chips is "signal amplification". When PCIe signals attenuate during long-distance transmission, Retimers receive, reconstruct, and

retransmit the signals to ensure data integrity. When a server adopts a modular design with CPUs and GPUs distributed on different boards, long-distance signal transmission

must rely on Retimers. If the CPU and GPU are on the same large motherboard, the signal link is shorter, and the number of Retimers used will decrease.

In short, as developers optimize software stacks around NVLink and cloud service providers deploy NVLink clusters in bulk, the living space of PCIe Retimers will be systematically

squeezed.

Furthermore, the chain reaction of ecosystem migration is even more disruptive. Intel will customize x86 CPUs for NVIDIA, and these chips will directly integrate NVLink interfaces

into AI infrastructure platforms—which means part of the PCIe server market will shift to the NVLink architecture.

Previously, to promote a proprietary protocol to become an industry standard and compete against the open PCIe Consortium, NVIDIA alone had achieved considerable results,

but it was ultimately a lonely battle that could not be sustained. In this grand strategy, Intel is precisely the most critical and subtle "chess piece". Once Intel's server CPUs start

supporting NVLink, the entire server ecosystem will be forced to follow suit, which will greatly accelerate the popularization of NVLink and establish it as a de facto industry

standard.

If this solution is truly successful, it is easy to imagine that future AI server designs, motherboard layouts, and chip interfaces will all be built around NVLink. Any chip (whether

CPU or other AI chip) that wants to access this high-performance computing ecosystem must be compatible with the NVLink Fusion protocol. This will form a powerful bundling effect, firmly locking the entire industrial chain—from motherboard manufacturers and server vendors to end users—into NVIDIA's ecosystem. Once NVIDIA gains control over the

protocol, it can profit from every piece of hardware connected to its ecosystem through authorization, certification, and other means, becoming the "Qualcomm" of the data

center era.

At first glance, NVIDIA's move to "invest in Intel" seems like a gesture of goodwill or penetration from the GPU leader to the CPU giant, aiming to complete its landscape in the

general computing field. However, this is not just an investment; it is a far-reaching layout intended to reshape the underlying protocols of future data centers and build a second

"moat" for NVIDIA beyond CUDA—an forward-looking arrangement for the NVLink interconnection protocol.

The essence of this impact is a paradigm shift in industry standards from "universal compatibility" to "vertical integration". When the leading manufacturers of CPUs and GPUs

directly define interconnection protocols, the value of third-party Retimer chips will naturally shrink significantly, and the restructuring of the market pattern may already be on the horizon.

From another perspective, the cooperation between NVIDIA and Intel also has advantages in terms of strategic synergy: in the face of common challenges (such as the erosion of the ARM architecture in the server market, and AMD's expansion in the CPU and GPU fields), Intel and NVIDIA can form an "nvtel alliance" focusing on "CPU+GPU/interconnection"

to jointly define the architecture of the next-generation computing platform.

Final Thoughts

Overall, when NVIDIA invested in Intel with its NVLink technology and used the strategic upgrade of "defining a moat through protocols" to reshape the architectural pattern of

high-performance computing, the PCIe Retimer market has indeed bid farewell to its previous golden age of "unassailable high-speed growth". This interconnection revolution

jointly initiated by the two chip giants may temporarily impact Retimer chips that have established a firm foothold relying on PCIe links.

However, this is only a preliminary observation. Because in the view of many analysts, the market space for PCIe Retimers is still rooted in many scenarios that cannot be fully

covered by NVLink. In long-distance transmission and complex topologies, the copper cable connections between the front and rear ends of GPU servers, as well as between

GPUs and switches, still require Retimers to offset signal attenuation with their adaptive equalization capabilities. In the field of non-GPU device interconnection, for high-speed

links between SSDs, network cards, and CPUs—especially in complex wiring scenarios—Retimers remain the key to ensuring "zero packet loss" of data. Not to mention servers

adopting the OAM architecture, whose universal baseboard (UBBP) design inherently relies on Retimer chips to maintain signal integrity.

This irreplaceability ensures that the PCIe Retimer market still has a solid foundation, and it remains an "indispensable piece of the puzzle" in the computing power network of the AI era.

11:03:41